- 您现在的位置:买卖IC网 > Sheet目录2004 > LTC1597AIN#PBF (Linear Technology)IC CONV D/A 16BIT PAR 28-DIP

11

LTC1591/LTC1597

15917fa

Table 1

CONTROL INPUTS

CLR

WR

LD

REGISTER OPERATION

0

X

Reset Input and DAC Register to All 0s for LTC1591/LTC1597 and Midscale for LTC1591-1/LTC1597-1 (Asynchronous Operation)

1

0

Load Input Register with All 14/16 Data Bits

1

Load DAC Register with the Contents of the Input Register

1

0

1

Input and DAC Register Are Transparent

1

CLK = LD and WR Tied Together. The 14/16 Data Bits Are Loaded into the Input Register on the Falling Edge of the CLK and Then

Loaded into the DAC Register on the Rising Edge of the CLK

1

0

No Register Operation

TRUTH TABLE

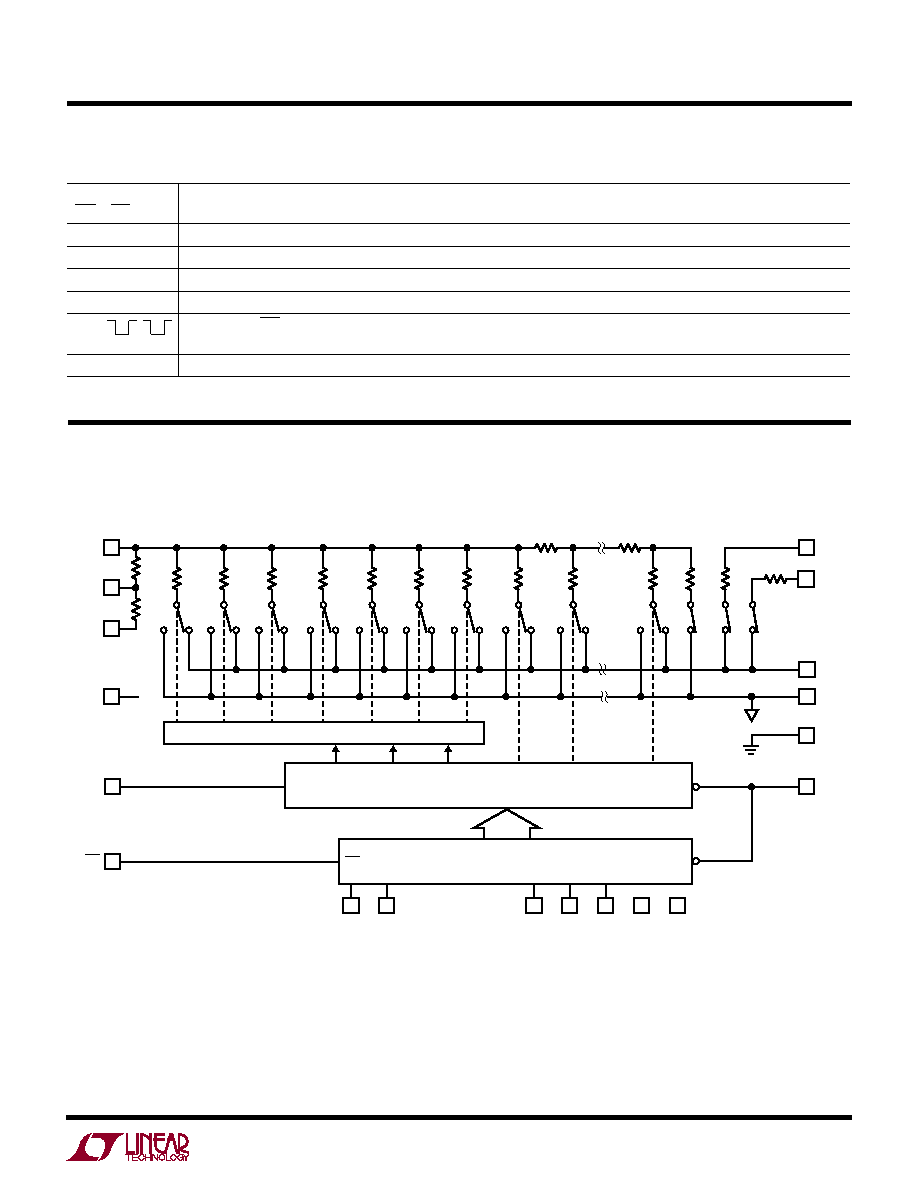

BLOCK DIAGRA SM

W

LTC1591

96k

12k

96k

48k

96k

48k

96k

DECODER

D13

(MSB)

D11

D12

D13

D10

D9

D0

(LSB)

LOAD

VCC

REF

RFB

IOUT1

AGND

CLR

28

DGND

22

1591 BD

DAC REGISTER

48k

12k

8

23

R1 3

RCOM 2

1

LD

9

10

D12

11

D2

21

D1

24

D0

25

NC

27

NC

26

WR

7

6

5

ROFS

4

12k

WR

INPUT REGISTER

RST

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC1598CG

IC A/D CONV 12BIT SRL 8CH 24SSOP

LTC1598LCG

IC A/D CONV 12BIT SRL 8CH 24SSOP

LTC1599AIG#TRPBF

IC D/A CONV 16BIT MLTPLYNG24SSOP

LTC1603IG#TRPBF

IC ADC W/SHUTDOWN 16BIT 36-SSOP

LTC1604AIG#TR

IC ADC 16BIT SAMPL SHTDWN 36SSOP

LTC1605-1IN#PBF

IC A/D CONV 16BIT SAMPLNG 28-DIP

LTC1605AISW#TR

IC ADC 16BIT 5V SAMPLING 28SOIC

LTC1606AISW#TRPBF

IC A/D CONV 16BIT SAMPLNG 28SOIC

相关代理商/技术参数

LTC1597BCG

功能描述:IC D/A CONV 16BIT PAR 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BCG#PBF

功能描述:IC D/A CONV 16BIT PAR 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BCG#TR

功能描述:IC DAC 16BIT PAR 28SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BCG#TRPBF

功能描述:IC D/A CONV 16BIT PAR 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BCN

制造商:Linear Technology 功能描述:DAC 1-CH R-2R 16-bit 28-Pin PDIP N

LTC1597BCN#PBF

功能描述:IC CONV D/A 16BIT PAR 28-DIP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BIG

功能描述:IC D/A CONV 16BIT PAR 28-SSOP RoHS:否 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k

LTC1597BIG#PBF

功能描述:IC D/A CONV 16BIT PAR 28-SSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 产品培训模块:Data Converter Fundamentals

DAC Architectures 标准包装:750 系列:- 设置时间:7µs 位数:16 数据接口:并联 转换器数目:1 电压电源:双 ± 功率耗散(最大):100mW 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-LCC(J 形引线) 供应商设备封装:28-PLCC(11.51x11.51) 包装:带卷 (TR) 输出数目和类型:1 电压,单极;1 电压,双极 采样率(每秒):143k